Did you mean: HT80

- APPLICATION NOTE AN1108

- Advanced Linear Devices

- Electrically Programmable Analog Device (Epad) Applications

- APPLICATION NOTE AN17

- Advanced Linear Devices

- Using Low Voltage Fet Input Operational Amplifiers

- APPLICATION NOTE AN1700

- Advanced Linear Devices

- User Programmable Offset Voltage (VOS) of Epad Operational Applications

- APPLICATION NOTE AN4200

- Advanced Linear Devices

- CMOS 5 Volt/3 Volt Analog Switch Applications

- APPLICATION BRIEF

- Altera Corporation

- AB 131: State Machine Encoding

- APPLICATION NOTE

- Advanced Micro Devices

- Designing for EMI Compliance

- APPLICATION NOTES

- Atmel Corporation

- T90FJR (CIMaX)

- AVR APPLICATION NOTE

- Atmel Corporation

- AVR202: 16-Bit Arithmetics

- BLUETOOTH APPLICATION NOTES-WHITEPAPERS

- Atmel Corporation

- Bluetooth Qualification Procedure White Paper

- BLUETOOTH APPLICATION NOTES/WHITEPAPERS

- Atmel Corporation

- Bluetooth General Information White Paper

- CELL-BASED ASICS - APPLICATION NOTES

- Atmel Corporation

- ASIC Design Guidelinges , This document constitutes a general set of recommendations intended for use by designers when preparing circuits for fabrication by Atmel. The guidelines are independent of any particular CAD tool or silicon process. They are a

- EPROM - APPLICATION NOTES

- Atmel Corporation

- The Benefits of Atmels RAPID Programming Algorithm , This Application Note details the Atmel RAPID programming algoarithm and briefly explains why this algorithm is superior to others. In addition, it will give an introduction to EPROM technology and th

- FIELD PROGRAMMABLE GATE ARRAY (FPGAS) - APPLICATION NOTES

- Atmel Corporation

- Implementing Cache Logic with FPGAs , This Application Note describes our enabling technology to make adaptive hardware possible for electronics systems.

- FLASH MEMORY - APPLICATION NOTES

- Atmel Corporation

- Recommended Reprogramming Procedure for Atmels Flash Memories , This Application Note describes the recommended reprogramming procedure for some of Atmels flash memories

- FPGA APPLICATION NOTE

- Atmel Corporation

- Symmetrical 24-tap FIR Filter Macro (FIR24S)

- FPGA CONFIGURATION MEMORY - APPLICATION NOTES

- Atmel Corporation

- C Routines for the AVR Microcontroller-AT17CXXX ISP Code

- FPSLIC APPLICATION NOTE

- Atmel Corporation

- Designing in Split Power Supply Support for AT94KAL-AX and AT94SAL-AX Devices

- FPSLIC - APPLICATION NOTES

- Atmel Corporation

- Mixing C and Assembly Code with IAR Embedded Workbench for FPSLIC , This Application Note describes how to use C to control the program flow and main program and assembly modules to control time-critical I-O functions.

- GATE ARRAYS-EMBEDDED ARRAYS - APPLICATION NOTES

- Atmel Corporation

- Converting FPGAs and PLDs to Atmel Gate Arrays , This Application Note discusses some factors to consider when deciding to convert, describes the conversion process, and details the required information for selected FPGA and PLD products.

- PARALLEL EEPROM - APPLICATION NOTES

- Atmel Corporation

- Software Chip Erase , Atmel EEPROMs feature Software Chip Erase which allows erasure of the entire memory contents in one step using a 6-byte code.

- POWER METERING - APPLICATION NOTES

- Atmel Corporation

- Power Metering Front End Design: The Delta Connection , This Application Note describes how to implement the chipset in three-phase, three-wire environments.

- PROGRAMMABLE SLI APPLICATION NOTE

- Atmel Corporation

- IP Core Generator: Constant

- APPLICATION BOARD WITH BLUETOOTH

- Bosch

- APPLICATION BOARD WITH BLUETOOTH

- APPLICATION BOARD WITHOUT BLUETOOTH

- Bosch

- APPLICATION BOARD WITHOUT BLUETOOTH

- APPLICATION BOARD WITH BLUETOOTH

- Bosch

- APPLICATION BOARD WITH BLUETOOTH

- APPLICATION BOARD WITHOUT BLUETOOTH

- Bosch

- APPLICATION BOARD WITHOUT BLUETOOTH

- CMX867 APPLICATION NOTE

- Cml Microcircuits

- CMX867 - V.22 Full-Duplex Call Set-up on the CMX867

- CMX868 APPLICATION NOTE

- Cml Microcircuits

- CMX868 - Programmers Quick Reference

- APPLICATION NOTE TAN-017

- Exar Corporation

- XRT7300 DS3-E3-STS-1 LIU IC Power Conditioning Requirements

- APPLICATION NOTE TAN-042

- Exar Corporation

- Designing the XRT71D00 and the XRT73L00 Devices to Operate in the Host Mode, and to be Accessed via a Single Chip Select Pin.

- APPLICATION NOTE TAN-046

- Exar Corporation

- XRT73L04 4-Channel DS3-E3-STS-1 LIU IC Power Conditioning Requirements

- CLOCK APPLICATION NOTE

- Exar Corporation

- General Application Note for ST49Cxxx Clock Family

- RCY21151WA1

- Fohrenbach Application Tooling

- RCY21151WA1

- RCY21234A2

- Fohrenbach Application Tooling

- RCY21234A2

- APPLICATION NOTES

- Infineon Technologies

- BTS780GP Replacement

- APPLICATION NOTE 80

- Linear Technology

- How to Use the Worlds Smallest 24-Bit No Latency Delta-SigmaTM ADC to its Fullest Potential

- APPLICATION NOTE 86

- Linear Technology

- A Standards Lab Grade 20-Bit DAC with 0.1ppm-°C Drift

- APPLICATION NOTE 88

- Linear Technology

- Ceramic Input Capacitors Can Cause Overvoltage Transients

- MAX6100EUR APPLICATION NOTE

- Maxim Integrated Products, Inc.

- Reliability Report

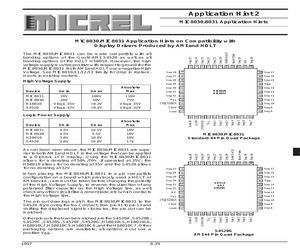

- APPLICATION HINT 02

- Micrel Semiconductor, Inc.

- MIC8030 Application Hints (MIC8030)

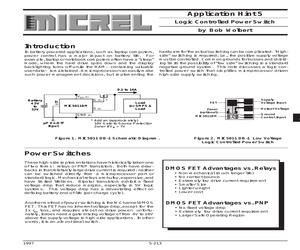

- APPLICATION HINT 05

- Micrel Semiconductor, Inc.

- Logic Controlled Power Switch (MIC5011)

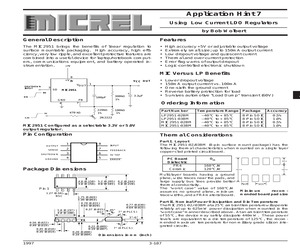

- APPLICATION HINT 07

- Micrel Semiconductor, Inc.

- Using Low-Current LDO Regulators (MIC2951)

- APPLICATION HINT 09

- Micrel Semiconductor, Inc.

- Low-Voltage Operation of the MIC5014 Family (MIC5014)